This introductory post aims at discussing a bit about business model of ARM ltd.(that's right the company behind ARM architectures!!), different ARM architectures for different utilities and most importantly a brief about ARM cortex M , ARM cortex R and ARM cortex A.

|

| ARM |

So, here's the content:

- Business model of ARM ltd.

- ARM Terminology

- Different ARM Architectures and Families

- Third party ARM variants

- ARM cortex M

- ARM cortex R

- ARM cortex A

ARM Ltd.

ARM ltd. was founded late in 1990's as a joint venture between Acorn computers , Apple computers(Apple Inc.) and VLSI technology Inc.

|

| ARM joint venture |

With it's headquarters in Cambridge, UK, ARM manages to be one of the top notch processor designing companies.

Unlike most traditional microprocessor suppliers, such as Intel, Freescale Arm only creates and licenses its technology as intellectual property (IP), rather than manufacturing and selling its own physical CPUs, GPUs, SoCs or micro controllers.It supplies system level ip, physical level ip as well as development tools(like KEIL) for their products.

Terminologies:

Micro-architectures:

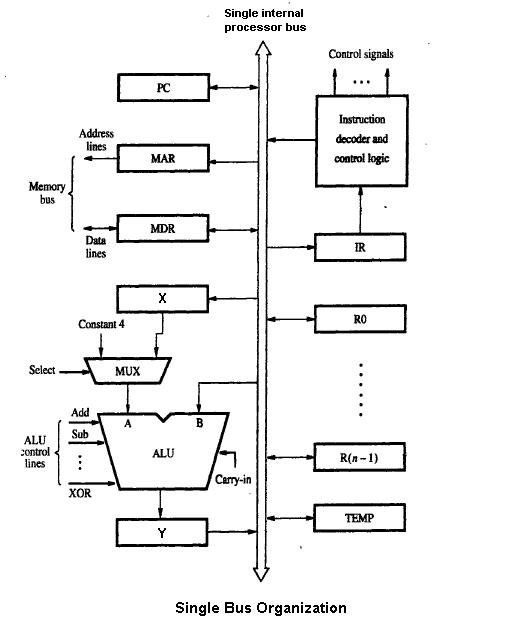

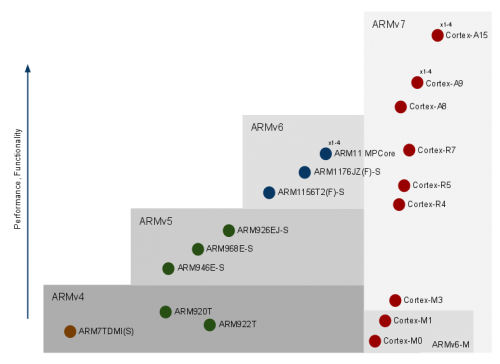

Micro-architecture or computer organization is a way of implementing an Instruction set architecture in a particular processor.

The ISA is roughly the same as the programming model of a processor as seen by an assembly language programmer or compiler writer. The ISA includes the execution model, processor registers,

address and data formats among other things.

|

| Image courtesy:arm university program |

The micro-architecture

includes the constituent parts of the processor and how these

interconnect and inter operate to implement the ISA.

Different aspect of micro architecture includes:

- Increasing execution speed

- Instruction set choice

- Instruction pipelining

- Multiprocessing and multi threading etc.

Different types of micro architectures include Harvard and Von Neumann architectures.

Intel i4 uses Haswell µarch and i7 uses Skylake architecture.

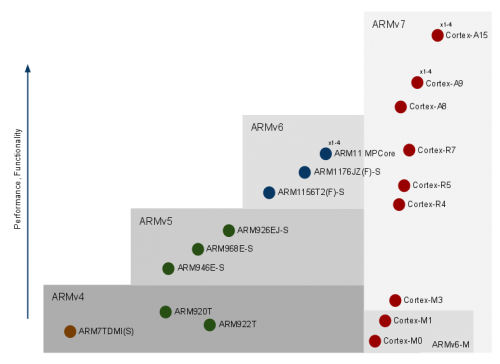

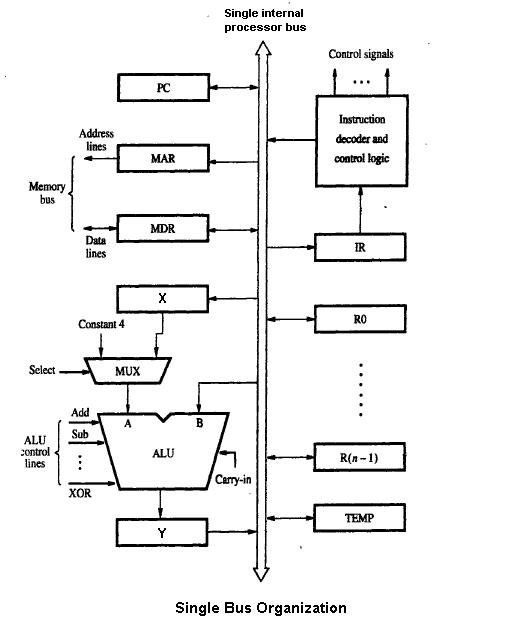

Architecture, Family and Cores :

The

architectures are the specifications, i.e. the set of registers, instructions and operation modes that should be supported by implementations of the architecture.

A

family is a specific detailed implementation of an architecture, i.e. the

actual hardware details needed to create an ARM core.

|

| Image courtesy:arm university program |

Finally a

core is a specific implementation of an architecture, i.e. the actual

blue-print of the transistors and other discrete parts needed to create a ARM CPU.

The ARM architectures are modular so families may implement only some features of the architecture and not others. Families may also have extensions not in the architecture and to make things even more interesting cores in the same family will usually differ in the features they support.

ARM11 and ARM Cortex-M are different families implementing features in the ARMv6 architecture with different markets in mind: ARM-11 smart phones and tablets and Cortex-M micro-controllers.

| Family |

Architecture versions implemented |

Example of processors |

| Arm1 |

Armv1 |

Arm1 |

| Arm2 |

Armv2 |

Arm2 |

|

Armv2a |

Arm250 |

| Arm3 |

Armv2a |

Arm3 |

| Arm6 |

Armv3 |

Arm60, Arm600, Arm610 |

| Arm7 |

Armv3 |

Arm700, Arm710, Arm710a |

|

Armv4T |

Arm7TDMI, Arm710T, Arm720T |

| ... |

... |

... |

| Cortex-A |

Armv7-A |

Cortex-A5, Cortex-A8, Cortex-A9 |

| Cortex-R |

Armv7-R |

Cortex-R4 |

| Cortex-M |

Armv6-M |

Cortex-M0, Cortex-M1 |

|

Armv7-M |

Cortex-M3 |

|

Armv7-ME |

Cortex-M4 | | |

Link:

https://en.wikipedia.org/wiki/List_of_ARM_microarchitectures

|

| Image courtesy:arm university program |

Different ARM architectures and Families

|

| Image courtesy: www.arm.com |

Third Party ARM variant:

- Snapdragon, by Qualcomm

- Ax, by Apple

- Exynos, by Samsung

- Denver, by Nvidia

- K12, by AMD

- StrongArm, by Digital Corp. etc.

ARM Processor Families:

ARM7

- It is introduced in 1994 (ARM7TDMI, ARM7EJ-S, ARM720T)

- Arm7 family has been immensely successful & has established ARM as the architecture of choice in digital word.

|

| Image courtesy: www.arm.com |

- Features:

- Pipeline Depth: 3 stage (Fetch, Decode, Execute)

- Operating frequency: 180 MHz

- Power Consumption: 0.06 mW/MHz.

- MIPS/MHz: 0.97

- Architecture used: Von-Neumann

- MMU/MPU, Cache: Not present

- Jazelle Instruction: Not present

- Thumb Instruction: Yes (16 bit instruction set)

- ARM Instruction set: Yes (32 bit)

- ISA (Instruction Set Architecture): V4T (4 TH Version)

- Interrupt Controller: Not Present

ARM9

- This family enables single processor solution for

microcontroller, DSP & JAVA applications, offering savings in chip

area & complexity, power consumption & time to market

- ARM9 – enhanced processors are well suited for applications requiring a mix of DSP+ Microcontroller performance

- ARM9 family includes – ARM926EJ-S, ARM946E-S, & ARM968E-S processors.

- Features:

|

| Image courtesy: www.arm.com |

- Pipeline Depth: 5 stage (Fetch, Decode, Execute, Decode, Write)

- Operating frequency: 150 MHz

- Power Consumption: 0.19 mW/MHz

- MIPS/MHz: 1.1

- Architecture used: Harvard

- MMU/MPU: Present

- Cache Memory: Present (separate 16k/8k)

- ARM/ Thumb Instruction: Support both

- ISA (Instruction Set Architecture): V5T(ARM926EJ-S)

- 31 (32-Bit size) Registers

- 32-bit ALU & Barrel Shifter

- Enhanced 32- bit MAC block

- Memory Controller

Memory operations are controlled by MMU or MPU

- MMU:

- Provides Virtual Memory Support

- Fast Context Switching Extensions

- MPU:

- Enables memory protection & bounding

- Sand – boxing of applications

- Flexible Cache Design (sizes can be 4KB to 128KB)

- DSP Enhancements

- Single cycle 32x16 multiplier Implementation

- Speed up all the multiply instructions

- New 32x16 & 16x16 multiply instructions

ARM11

- It delivers low power & a range of performance from 350MHz to 1GHz.

- ARM11 processor software is compatible with all previous generations of ARM processors.

- It introduces 32-bit SIMD for media processing

- Physically tagged caches to improve OS context switch performance.

- Trust zone for H/W enforced security.

- Tightly coupled memories for real-time applications.

- ARM1176JZ (F)-S & ARM11MP core, ARM1136J(F)-S, ARM1156T2-S processor.

- Features:

- Pipeline Depth: 8stage

- Operating frequency: 335MHz.

- Power Consumption: 0.4mW/MHz.

- MIPS/MHz: 1.2

- Architecture used: Harvard

- MMU/MPU: Present

- Multiplier unit: 16x32 (16 bits of 32-bit size register)

- Cache Memory: present (4-64k size)

- Powerful ARMV6 instruction set architecture

- Supports the thumb instruction set-memory BW & Size requirements reduces by up to 35%

- Supports Jazelle Technology for efficient embedded JAVA execution

- Supports the DSP extensions

- SIMD media processing extensions deliver up to 2x performance for video processing

- ARM Trust-Zone Technology for on chip security

- Thumb-2 Technology for enhanced performance energy efficiency & code density

- High performance integer processor

- Vectored interrupt interface & low-interrupt latency mode speeds up interrupt response & real time performance

- Optional vector floating point co-processor for automotive/ industrial controls & 3D graphics acceleration.

Cortex-M

|

| Image courtesy: www.arm.com |

Cortex M4 32 bit processor family is build extensively for micro controller applications. It includes following features:

- Ultra low power consumption with sleep and deep sleep mode.

- Faster interrupt handling, normally achieved via NVIC(Nested vector interrupt controller) which provides 256 interrupt priority levels and supports up to 240 external interrupts.

- Improved security via MPU(Memory protection unit) which defines access rules and privilege modes for certain regions of memory, so that no unauthorized piece of code can overwrite that region of memory.

- Faster calculations on Floating point numbers via FPU.

- 3 stage pipelined Harvard architecture

- Hardware debug via JTAG or Serial wire debug(SWD).

- Implements Thumb 2 instruction set

Cortex A8

|

| Image courtesy: www.arm.com |

Cortex A series is widely used for application specific purposes like mobile phones, Single board computers etc.

Cortex A8 includes 5 different instruction sets namely, Arm, Thumb, Neon, TrustZone, floating point(for floating point arithmetic).

TrustZone technology divides both hardware and software into two non -overlapping regions i.e secure and non-secure region. Hardware segregation ensure that no information is leaked between these two worlds, thus providing a very efficient defense mechanism for numerous memory leakage, stack overflow based attacks.

|

| Trust Zone technology |

Neon on the other hand is an advanced SIMD(single instruction multiple data) extension which includes instructions for signal processing, data integrity etc.

ARM provides neon libraries which can be used to carry out various operations like fft using NEON hardware set.

|

| Image courtesy: www.arm.com |

The Cortex-A8 implements the extended ISA in the first ever fully

superscalar design from Arm. It has a full dual-issue pipeline, meaning

the Cortex-A can simultaneously issue any two instructions that occur

sequentially in the instructions stream whose arguments do not have

unresolved dependencies.

It has the ability to scale in speed from

600MHz to greater than 1GHz, meeting the requirements for

power-optimized mobile devices needing operation in less than 300mW and

performance-optimized consumer applications.

Cortex R5

|

| Image courtesy: www.arm.com |

Cortex R series is developed specifically for time critical real time applications like Car on-board computing unit, space flight control etc.

It has significantly better reliability then Cortex M/A due to multiple error checking and correcting(ECC) units.

It features 8 stage pipelining with Harvard memory architecture and optional TCM(Tightly Coupled Memory) for very low latency applications.

LLPP(Low latency peripheral port) features interconnection between peripherals via 32 bit AMBA AXI/AHB bus.

References:

- https://developer.arm.com/products/processors/cortex-r/cortex-r5/docs

- http://whatis.techtarget.com/definition/ARM-processor

- https://en.wikipedia.org/wiki/List_of_ARM_microarchitectures

- https://www.design-reuse.com/articles/26106/cortex-r-versus-cortex-m.html

- http://www.differencebetween.net/technology/difference-between-ahb-and-axi/

- https://developer.arm.com/technologies/trustzone

- https://developer.arm.com/technologies/neon

Do let me know in case of any query/feedback, would love to hear one!

If you like it don't forget to share it.

Comments

Post a Comment